文章来源:半导体与物理

原文作者:jjfly686

本文介绍了CMOS工艺中第一层互联的作用、材料及工艺步骤。

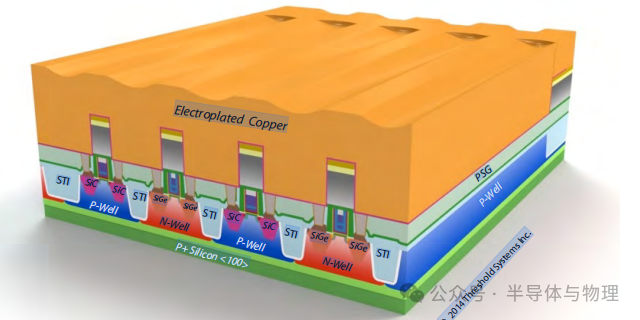

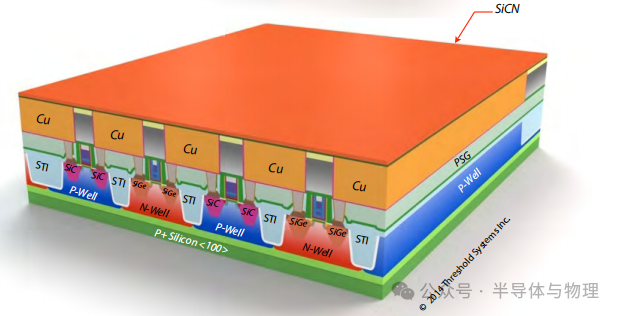

芯片中的晶体管(如NMOS和PMOS)需要通过金属线连接才能形成完整电路。第一层互联(通常称为M0或Local Interconnect)是直接连接晶体管源极、漏极和栅极的金属层,位于晶体管上方,距离硅衬底仅几十纳米。它的核心任务是在器件层建立最短、最密集的连接通道,避免信号绕行到高层金属,从而提升芯片性能和集成密度。

第一层互联的结构与作用

以最简单的CMOS反相器为例(如下图),NMOS和PMOS的漏极与源极需要通过金属线直接相连:

物理结构:

NMOS漏极(A)与PMOS源极(C)通过第一层铜线(B)直接连接,形成输出端;

栅极(Input)通过多晶硅或金属线接收输入信号;

电源(Vdd)和地线(GND)通过局部互连分别连接到PMOS和NMOS。

缩短路径:信号直接在晶体管间传输,无需绕行至更高层金属(如M1-M10),延迟降低15%-20%;节省面积:在7 nm芯片中,第一层互联使逻辑单元面积缩小30%以上;简化设计:减少布线交叉点,降低电路复杂度。

材料与工艺

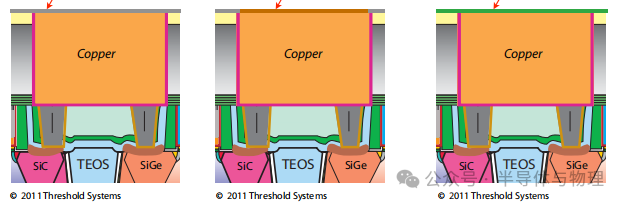

第一层互联的金属线宽度通常在10-30 nm(约为头发丝的万分之一),需采用特殊材料和工艺:铜(Cu):电阻率低(1.68 μΩ·cm),但需搭配氮化钽(TaN)阻挡层防止铜扩散;钴(Co):在5 nm以下节点逐步替代铜,填充深宽比>5:1的纳米沟槽时无空隙缺陷;阻挡层:2 nm厚的钽(Ta)或钛(Ti),增强金属与介质层的结合力。

工艺步骤

刻蚀沟槽:在氧化层中刻蚀出纳米级凹槽(深度50-100 nm,宽度10-20 nm);沉积阻挡层:用物理气相沉积(PVD)或原子层沉积(ALD)生成2 nm厚的TaN;铜种子层与电镀:PVD沉积铜种子层,电镀填充铜;化学机械抛光(CMP):磨平表面,确保金属线平坦化。

- 随机文章

- 热门文章

- 热评文章

- 人间烟火气,蜀中蓉小香——成都老味蓉小香冒烤鸭

- 售15.59万起/5款配置 长安启源A07上市

- 第二届全球数字生态大会数字会展在杭州成功举办

- 新门派峨眉!《剑侠世界:起源》峨眉论剑资料片今日8点上线

- 春立医疗取得3D打印骨连接棒系统专利,新骨生长提供充足的支撑

- 中国旭阳集团(1907.HK)获纳入MSCI全球小型股指数之中国指数

- 美股明年如何投资?富国银行给出建议:卖中小盘股、坚守大盘股

- 强生(JNJ.US)10亿美元引进口服多肽积极试验结果公布